在逻辑设计领域,只涉及单个时钟域的设计并...尤其对于一些复杂的应用,FPGA往往需要和多个时钟域的信号进行通信。异步时钟域所涉及的两个时钟之间可能存在相位差,也可能没有任何频率关系,即通常所说的不同频不同相。

”FPGA 跨时钟域信号 专用握手信号 文章 单片机 FPGA“ 的搜索结果

在逻辑设计领域,只涉及单个时钟域的设计并...尤其对于一些复杂的应用,FPGA往往需要和多个时钟域的信号进行通信。异步时钟域所涉及的两个时钟之间可能存在相位差,也可能没有任何频率关系,即通常所说的不同频不同相。

文章目录前言一、电平信号的跨时钟域处理二、使用步骤1.引入库2.读入数据总结 前言 单bit信号的跨时钟域处理,可以分为电平信号的跨时钟域处理和脉冲信号的跨时钟域处理。 一、电平信号的跨时钟域处理 电平信号,...

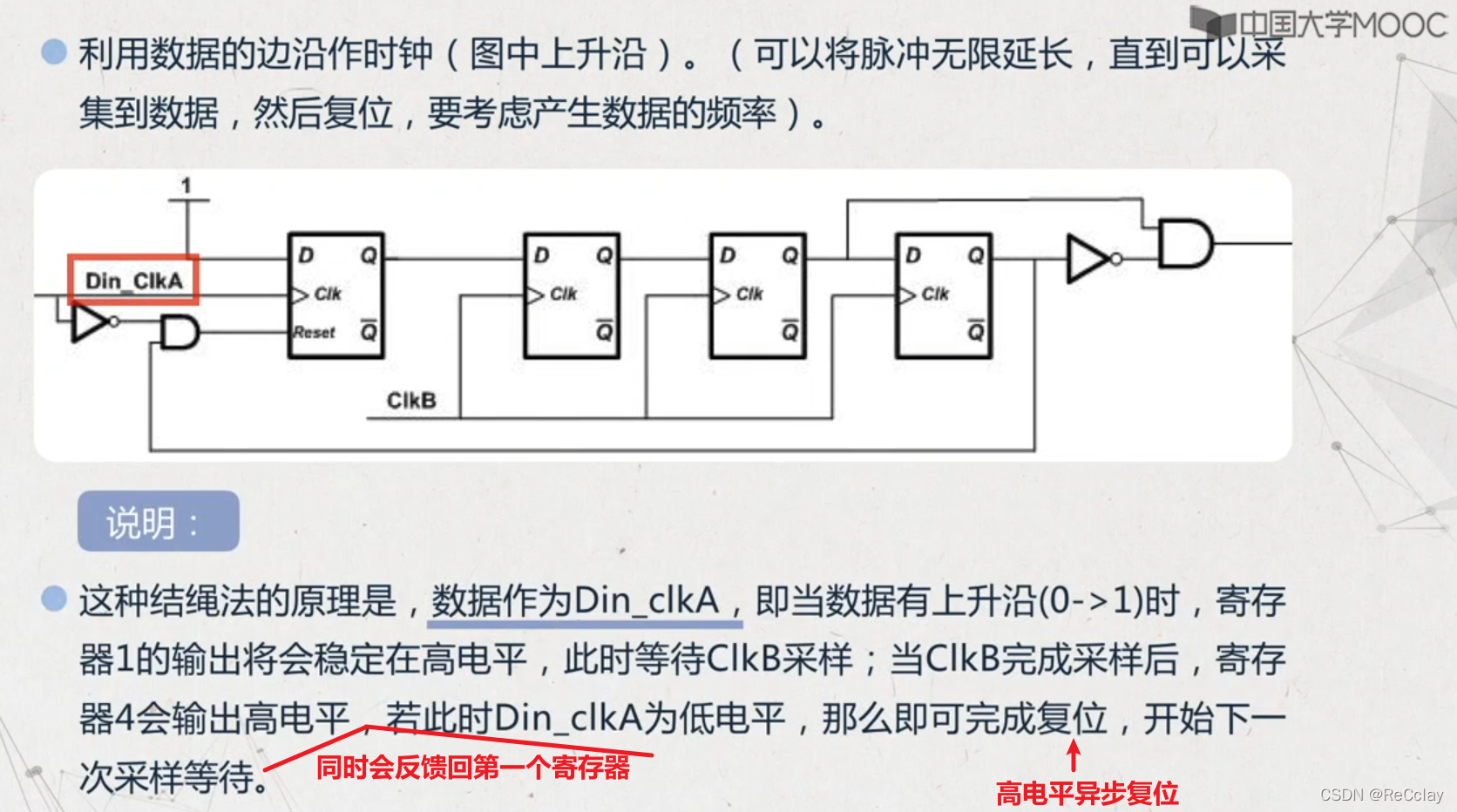

文章目录一、同步——慢时钟域到快时钟域一、同步——快时钟域到慢时钟域 一、同步——慢时钟域到快时钟域 脉冲同步器的基本原理: 将src_clk时钟域的输入脉冲转换为src_clk时钟域的电平信号src_state; 对src_...

跨时钟域(CDC:Clock Domain Crossing)的信号可以分为单bit信号和多bit信号。 一、单bit信号跨时钟域的处理方法 1. 慢时钟域到快时钟域 两级触发器同步 频率相差2倍以上,不用考虑快时钟域信号采样丢失,使用两级...

由于寄存器在任何信号通路中都有特定的建立时间和保持时间,这要求输入信号要保持稳定。但如果信号在这段时期发生了变化,那么输出将是未知的。这个未知的状态便称为亚稳态。 危害 只要系统中存在异步元件,那么亚...

分别编写一个数据发送模块和一个数据接收模块,模块的时钟信号分别为clk_a,clk_b。两个时钟的频率不相同。数据发送模块循环发送0-7,在每个数据传输完成之后,间隔5个时钟,发送下一个数据。请在两个模块之间添加...

我在两年前通过自学跨行社招加入了IC行业。在前几篇文章里,我们讨论了通过建立时间和保持时间,来进行时序分析,并介绍了同步电路中如果建立时间或保持时间违例,该如何修复。本篇文章主要讨论异步电路中,该如何...

文章目录一、full_handshake_rx1.1 输入输出信号1.2 代码逻辑二、full_handshake_tx2.1 输入输出信号2.2 代码逻辑三、跨时钟域传输总结 受一位朋友之邀写了这篇博客,讲解 tinyriscv 中的跨时钟域传输。 所解析的...

全国大学生电子设计大赛至今结束已有两个月,当时选了F题频率计设计,由于之前备赛的时候有参考过相关的论文,而且自身也有一点FPGA的基础,最主要的是FPGA做频率计原理简单,精度相对于用单片机来说高得多,于是...

什么是同步逻辑和异步逻辑? 时序设计的实质; 为什么触发器要满足建立时间和保持时间? 什么是亚稳态?为什么两级触发器可以防止亚稳态传播? 系统最高速度计算(最快时钟频率)和流水线设计思想

FPGA面试题整理1

标签: fpga开发

有关FPGA的简答题

1 数字IC(ASIC)设计流程:IC设计分为前端和后端。前端设计主要将HDL语言-->网表,后端设计是网表-->芯片版图。前端主要有需求分析与架构设计、RTL设计、仿真验证、逻辑综合、STA、形式验证。...

基于握手原理的,网上很多,这里记录一下自己亲测试了能用的(知乎上看的,自己稍微改了一下,他那个原版跨大时钟域就用不了了。

计算机通信的时钟信号,必须要,但不一定要传送

常见FPGA笔试题的概念总结

一种是握手,第二种是异步FIFO。 异步FIFO设计,一个是格雷码,第二个怎么判断空满信号。

推荐文章

- 大数据和云计算哪个更简单,易学,前景比较好?_大数据和云计算哪个好-程序员宅基地

- python操作剪贴板错误提示:pywintypes.error: (1418, 'GetClipboardData',线程没有打开的剪贴板)...-程序员宅基地

- IOS知识点大集合_ios /xmlib.framework/headers/xmmanager.h:66:32: ex-程序员宅基地

- Android Studio —— 界面切换_android studio 左右滑动切换页面-程序员宅基地

- 数据结构(3):java使用数组模拟堆栈-程序员宅基地

- Understand_6.5.1175::New Project Wizard_understand 6.5.1176-程序员宅基地

- 从零开始带你成为MySQL实战优化高手学习笔记(二) Innodb中Buffer Pool的相关知识_mysql_global_status_innodb_buffer_pool_reads-程序员宅基地

- 美化上传文件框(上传图片框)_文件上传框很丑-程序员宅基地

- js简单表格操作_"var str = '<table border=\"5px\"><tr><td>序号</td><-程序员宅基地

- Power BI销售数据分析_powerbi汇总销售人员业绩包括无销售记录的人-程序员宅基地